-

存储器(二):DRAM

一、DDR简述

1、概念

- SDR:Single Data Rate 单倍数据倍率

- DDR:Double Data Rate 双倍数据倍率

- QDR:Quad Data Rate 四倍数据倍率

- LPDDR:Low Power Double Data Rate 低功耗内存,是DDR的一种

- GDDR:Graphics Double Data Rate,是用于显卡显存的一种类型

SDR、DDR都是 SDRAM(Synchronous Dynamic Random-Access Memory), 相较于SDR只在时钟上升沿或下降沿进行数据传输,DDR特点是在时钟的上升沿与下降沿都进行数据传输,即一个时钟周期传输 2 拍数据,历代DDR提升速率方法如下:

DDR4采取将核心频率提高到200~400MHz,以提升总线速度

QDR 在保留 DDR 特征的基础上,升级了数据总线,DDR 只有 1 条数据通道,数据读/写操作共用,属于半双工工作方式,而 QDR 有 2 条独立数据通道,数据读/写操作可以同时进行,属于全双工工作方式,因此,QDR 的数据存取速率是 DDR 的两倍

2、I/O描述:

- DDR4 引脚按功能可以分为四大类:第一类为电源、地、校准;第二类为数据信号;第三类为时钟信号;第四类为控制、地址信号,分别如下表所示:

PIN Symbol Type Function 电源 VDD - 芯片主电源输入,1.2 V +/- 0.06 V VDDQ - DQ电源供电信号,1.2 V +/- 0.06 V VPP - DRAM激活电压,2.5V VREFCA - 控制/命令/地址信号的参考电平 地 VSS - 地 VSSQ - DQ信号参考地。 校准 ZQ - 阻抗匹配(ODT)的校准参考,外接240Ω1% 电阻到地 PIN Symbol Type Function 数据 DQL[0:7]、DQU[0:7] I |O 低8位数据和高8位数据信号线,共16位数据信号线 DML_n/DBIL_n I |O 低8位数据掩码 DMU_n/DBIU_n I |O 高8位数据掩码 DQSL_t/DQSL_c I |O 低8位数据选通信号 DQSU_t/DQSU_c I |O 高8位数据选通信号 PIN Symbol Type Function 时钟 CK_t/CK_c I 差分时钟输入信号,由DDR Controller输出 PIN Symbol Type Function 地址 BG[0:1] I Bank Group地址选择 BA[0:1] I Bank地址选择 A[0:16] I 地址选择信号,(其中 A10/AP,A12/BC_n,A14/WE_n,A15/CAS_n,A16/RAS_n有其它功能,A17仅用于16Gb) 控制 ALERT_n O 报警信号,若出现CRC错误或者命令/地址奇偶校验错误,该PIN脚拉低,告知DDR Controller TEN I 测试模式使能信号,高电平使能测试模式,正常操作过程中,弱下拉 RESET_n I DDR复位信号,低电平有效 PAR I 命令/地址信号的奇偶校验使能,可通过寄存器禁用或者使能 ODT I 阻抗匹配使能 CKE I 时钟信号使能,控制芯片是否进入低功耗模式 ACT_n I 命令激活信号,为低电平时,可以通过A[14:16]地址信号线选择激活命令的行地址;为高电平时,Address信号线正常使用 CS_n I DDR芯片Select,用于多个RANK时的RANK组选择

DDR的数据信号参考 DQS 选通信号,地址/控制信号参考 CK_t/CK_c 差分时钟信号;

二、物理格式

1、存储单元

A、基本存储单元

DRAM的基本存储单元(Storage Cell)采用的是晶体管控制电容充放电方法,电容充电代表1,电容(pF级别)放电代表0,实现 1bit 数据的读写。

如上图,只要给 MOS 管的栅极(Gate)高电平, MOS 管就会打开,电容中存储的电荷就会流入 BitLine 上,便可以进行信息的读取。

B、Memory Array

采用将多个 Storage Cell 组成一个二维阵列,可以实现更多信息的存储,即将同一行的所有MOS 管的栅极连接到同一根 WordLine上,把同一列的所有 MOS 管的源极连到同一根 BitLine 上,组成的 Memory Array (存储阵列)如下图所示:

可以看出,当我们要读出某一 Cell 存诸的信息时,需要给这一行的 WordLine 通高电平,这一行的 Cell 都将打开,每个 Cell 的电容器电平状态都将被加载到相应的 BitLine 上,也即能读出某个字中的所有位(bit)。一个字有多少位被称为字长,存储器中的字长和 CPU 的字长不太一致,如 64 位的 CPU,字长是 64,但在 DDR 存储器中,字长只有 4位、8位、16位。

实际应用中,由于 Cell 的电容值远小于 BitLine 线本身过长的引起的寄生电容值,导致很难可靠的识别 Cell 中的信息,因此采取差分存储思想,并将原来的参考零电平修改为 Vref,如下图所示

电容另一端电压为 VDD 时,此时其所存储的电荷

,即存储信息为 1;

,即存储信息为 1;电容另一端电压为 0 时,此时其所存储的电荷

,即存储信息为 0;

,即存储信息为 0;C、Differential Sense Amplifier

BitLine 也进行差分设置,两条 BitLine 在功能上完全等价,可以减小 Bit Line 的长度。

Differential Sense Amplifier 包含 Sensing Circuit 和 Voltage Equalization Circuit 两个主要部分。主要功能就是将 Storage Capacitor 存储的信息转换为逻辑 1 或 0 所对应的电压,并且呈现到 BitLine 上。同时,在完成一次读取操作后,通过 BitLine 将 Storage Capacitor 中的电荷恢复到读取之前的状态,基本电路如下图所示

D、Read Operation

一个完整的 Read Operation 包含 Precharge、Access、Sense、Restore 四个阶段

- Precharge

在这个阶段,首先会通过控制 EQ 信号,让 Te1、Te2、Te3 晶体管处于导通状态,将 Bitline 和 /Bitline 线上的电压稳定在 Vref 上,然后进入到下一个阶段;

-

Access

经过 Precharge 阶段, Bitline 和 /Bitline 线上的电压已经稳定在 Vref 上了,此时,通过控制 Wordline 信号,将 Ta 晶体管导通。Storage Capacitor 中存储正电荷会流向 Bitline,继而将 Bitline 的电压拉升到 Vref+,然后进入到下一个阶段。

-

Sense

由于在 Access 阶段,Bitline 的电压被拉升到 Vref+,Tn2 会比 Tn1 更具导通性,Tp1 则会比 Tp2 更具导通性。

此时,SAN (Sense-Amplifier N-Fet Control) 会被设定为逻辑 0 的电压,SAP (Sense-Amplifier P-Fet Control) 则会被设定为逻辑 1 的电压,即 Vcc。由于 Tn2 会比 Tn1 更具导通性,/Bitline 上的电压会更快被 SAN 拉到逻辑 0 电压,同理,Bitline 上的电压也会更快被 SAP 拉到逻辑 1 电压。接着 Tp1 和 Tn2 进入导通状态,Tp2 和 Tn1 进入截止状态。

最后,Bitline 和 /Bitline 的电压都进入稳定状态,正确的呈现了 Storage Capacitor 所存储的信息 Bit。

-

Restore

在完成 Sense 阶段的操作后,Bitline 线处于稳定的逻辑 1 电压 VDD,此时 Bitline 会对 Storage Capacitor 进行充电。经过特定的时间后,Storage Capacitor 的电荷就可以恢复到读取操作前的状态。

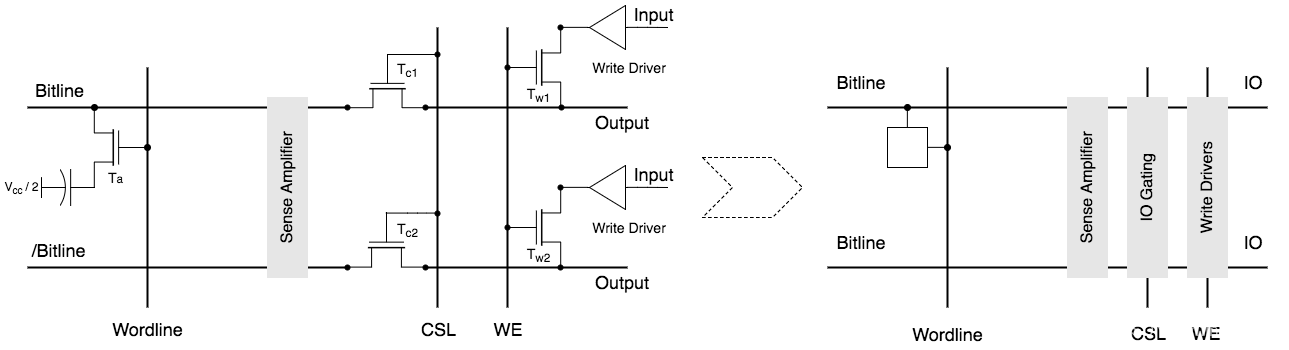

最后,通过 CSL 信号,让 Tc1 和 Tc2 进入导通状态,外界就可以从 Bitline 上读取到具体的信息。

E、Memory Organization

对差分存储 Storage Cell 进行抽象后,得到如下图所示的新结构图:

在不考虑形式的情况下,最简单的组织方式,就是在一个 Bitline 上,挂接更多的 Cells,如下图所示:

在实际制造过程中,并不会无限制的在 Bitline 上挂接 Cells。因为 Bitline 挂接 Cells 越多,Bitline 的长度就会越长,也就意味着 Bitline 的寄生电容值会更大,这会导致 Bitline 的信号边沿速率下降,导致性能的下降。 因此,可以把 Cells 分摊到 Bitline 差分对上,以减小 Bitline 的长度,如下图所示:

当两条 Bitline 都挂接了足够多的 Cells 后,如果还需要继续拓展,那么就只能增加 Bitline 了,增加后的结构图如下:

从图中可以看到,增加 Bitline 后,Sense Amplifier、Read Latch 和 Write Driver 的数量也需相应的增加,这意味着成本、功耗、芯片体积都会随着增加。因此,在实际的设计中,会优先考虑增加 Bitline 上挂接的 Cells 的数量,避免增加 Bitline 的数量,这也意味着,一般情况下 Wordline 的数量会比 Bitline 多。

上图是一个由 16 个 Cells 组成的 Memory Array。其中的控制信号有 8 个 Wordline、2 个 CSL、2 个 WE,一次进行 1 个 Bit 的读写操做,也可以理解为一个 8 x 2 x 1 的 Memory Array。

如果把 2 个 CSL 和 2 个 WE 合并成 1 个 CSL 和 1 个 WE,如下图所示。此时,这个 Memory Array 就有 8 个Wordline、1 个 CSL、1 个 WE,一次可以进行 2 个 Bit 的读写操作,也就是成为了 8 x 1 x 2 的 Memory Array。

按照上述过程,不断增加 Cells 数量,最终可以得到一个由差分存储组成的

的 Memory Array,如下图所示:

的 Memory Array,如下图所示:

其中,m 为 WordLine 的数量、n 为 CSL控制信号的数量、w 则为一次可以进行读写操作的 bits

例如存储阵列大小为 ,即通过控制 4 个行信号,2 个列信号,进行一次行列选通读写操作,可以同时选中 2 个 Storage Cell。

,即通过控制 4 个行信号,2 个列信号,进行一次行列选通读写操作,可以同时选中 2 个 Storage Cell。F、传输概念

- Burst Length:突发访问长度(BL)。

在打开的同一行中,将相邻的存储单元连续的进行数据传输,即只要指定起始行地址和列地址,控制器就会依次自动对后面相同的存储单元进行读/写操作,完成一次数据突发传输,而不需要控制器连续提供地址,称为 Burst。一行打开时连续读取的列数就是突发长度Burst Length。

DDR2 的 Burst Length 为 4;DDR3 的 Burst Length 为 8;DDR4 的 Burst Length 为 16;以 2Gb 256Mb x 8 颗粒为例,

DDR2一次突发传输可以传输 ,

,

DDR3一次突发传输可以传输 ,

,

DDR4一次突发传输可以传输

某DDR3颗粒,对Burst描述如下所示:

翻译一下:

DDR3 SDRAM的读取和写入访问是面向突发的。

访问从选定的位置开始,并按编程顺序继续访问编程数量的位置。

访问从ACTIVATE命令开始,然后跟着是READ或WRITE命令。

与ACTIVATE命令一起的地址位用于选择要访问的bank和row。

与READ或WRITE命令一起的地址位用于选择突发传输访问的bank和起始列位置。

- Prefetch:预取技术,协议称为 8n Prefetch,n为位宽。

以4颗 2Gb 256Mb x 8 DDR4 颗粒为例,4 颗DDR 颗粒的相同位置的 Bank是同时工作的,可在短时间内处理 4个128bit 的数据,称为Prefetch。

SDRAM开始是时钟下降沿采样,数据传输速率和频率是1:1关系,即一个周期可传输1bit数据

DDR1采用时钟双边沿采样,不需要提高时钟频率就能实现 2 倍的SDRAM速度(即预取2 bit),预读数为2n,各代 SDRAM 芯片的主要参数如下表所示:某DDR3颗粒,对Prefetch描述如下所示:标准 传输速率 核心频率 Prefetch 总线频率 最大位宽 电压 (V) SDR 100–166 100–166 1n 100–166 16/16 3.3 DDR 200–400 100–200 2n 100–200 16/32 2.5, 2.6 DDR2 400–1066 100–266 4n 200–533 16/64 1.8, 1.55 DDR3 800–2133 100–266 8n 400–1066 16/128 1.5, 1.35 DDR4 1600–3200 200–400 8n 800–1600 16/128 1.2 DDR5 4800-8400 300-525 16n 2400–4200 16/256 1.1

翻译一下:

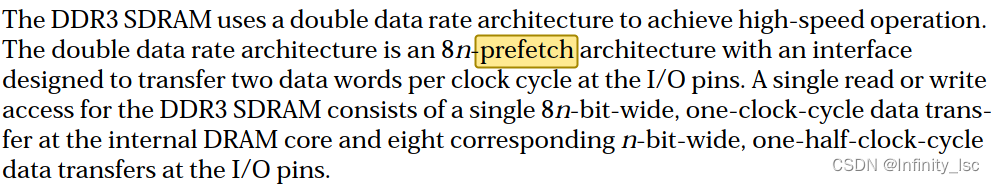

DDR3SDRAM使用双倍数据速率架构来实现高速操作。

双倍数据速率架构是具有8n-refetch架构的接口,该接口被设计为在每个时钟周期传输两个数据字的 l/O 引脚处。

DDR3 SDRAM 的单次读或写访问,由内部 DRAM 内核的单个 8 位宽、一个时钟周期数据传输和在 I/O 引脚上的8个相应的 n 位宽、半时钟周期数据传输组成

注

- 传输速率 (MT/s):为每秒发生的 Transfer 的数量,通常也是 DRAM 的标称速率,最常用,如 DDR3-800 中的 800 指的就是传输速率

- 核心频率 (MHz):DRAM 芯片内部控制逻辑和存储阵列的工作时钟的频率。

2、封装形式

DDR4 x4/x8/x16器件均为6个电气列,分为两组,每一组三个电气列,x4/x8格式为13行出球,x16为16行出球(不包括用于机械支撑的额外的非活动出球行),基于MO-207的出球策略示意图分别如下所示:

三、地址与内存

1、地址映射

DDR4颗粒在容量上有 4 种规格,分别为 2Gb、4Gb、8Gb 、16Gb(

);每种颗粒容量提供 3 种地址数量 x 位宽的组合, x4 、 x8 DRAM 有 4 个 Bank Group,x16 DRAM 仅有 2 个 Bank Group ,如下表所示:

);每种颗粒容量提供 3 种地址数量 x 位宽的组合, x4 、 x8 DRAM 有 4 个 Bank Group,x16 DRAM 仅有 2 个 Bank Group ,如下表所示:- 2 Gb Addressing Table

- 4 Gb Addressing Table

- 8 Gb Addressing Table

- 16 Gb Addressing Table

由上表可知,DDR4颗粒的地址线为行列复用,其中行地址数量是A0~A17,列地址数量是 A0~A9, Row、Bank、Bank Group (BG) 在不同位宽时是不同的。

2、容量计算

A、Data Width

Memory Array 的 Data Width 是指对该 Array 进行一次读写操作所访问的 Bit 位数。这个位数与 CSL 和 WE 控制线的组织方式有关。

B、Row

DRAM Memory 中的 Row 与 WordLine 是一一对应的,一个 Row 本质上就是所有接在同一根 Wordline 上的 Cells,如下图所示

DRAM 在进行数据读写时,选中某一 Row,实质上就是控制该 Row 所对应的 WordLine,打开 Cells,并将 Cells 上的数据缓存到 Sense Amplifiers 上。

Row Size

一个 Row 的 Size 即为一个 Row 上面的 Cells 的数量。其中一个 Cell 存储 1 个 Bit 的信息,也就是说,Row Size 即为一个 Row 所存储的 Bit 位数。C、Column

Column 是 Memory Array 中可寻址的最小单元。一个 Row 中有 n 个 Column,其中 n = Row Size / Data Width。下图是 Row Size 为 32,Data Width 为 8 时,Column 的示例

Column Size

一个 Column 的 Size 即为该 Column 上所包含的 Cells 的数量,与 Data Width 相同。Column Size 和 Data Width 在本质上是一样的,也是与 CSL 和 WE 控制线的组织方式有关3、计算实例

DDR4 的寻址由 BankGroup - Bank- Row - Column 组成,容量计算如下(以 2Gb 256Mb x 8 颗粒为例):

Bank Groups :4,即每个颗粒有 4 个Bank Group

BG Address:BG0~BG1,共 2 bit,即每个Bank Group 有个Bank

Rows:A0~A13,共14 bit,Total number of row =

Columns:A0~A9, 共10 bit,Total number of column =

Total DRAM Capacity =

即DDR颗粒有4个 Bank Group,每个bank Group有4个bank,每个bank有 的空间,每个空间存储 8 bit 数据

的空间,每个空间存储 8 bit 数据

其中,Page size = Column x 位宽 = 1K x 8bit= 1KB

四、系统组成

- DDR小系统由 DRAM颗粒、DDR PHY、DDR controller构成,其中DDR PHY和DDR controller一般集成在CPU/GPU中

- DIMM:Dual-Inline-Memory-Modules(双列直插式存储模块)

Rank:是一个逻辑概念,为一组内存颗粒位宽的集合,也称 Chips(例如一个内存颗粒的位宽是8bit,8个颗粒并联,可组成 64bit 位宽),可以被CPU的一个内存通道同时访问,Rank中的每个颗粒均共用地址线、控制线、数据线

DIMM、Rank、BankGroup,Bank关系如下图所示:

- DDR颗粒的数据线和控制&地址线连接示意图如下所示

以 64位 CPU,2Gb 256Mb x 8 颗粒为例:

64位CPU每次读写 64bit 数据,上图中,每颗 DDR为 8bit 位宽,将 8 颗 DDR 的数据线并联,可组成 64bit 的数据位宽,即一个Rank,CPU读写数据时,通过一次选取 8 颗 DDR 的同一个 bank 的相同行、相同列,便可实现一次读写 64bit 数据

五、数据传输

1、数据同步方式

数据传输中涉及到 3 种不同的同步方式:源同步、系统同步、自同步

- 源同步指 IC之间通信时,发送IC会生成一个伴随数据的时钟,接收IC使用此时钟进行数据接收,这种同步方式适用于短距离传输和高速传输,例如在计算机内部的数据传输。

- 系统同步指 IC之间通信时,外部公共时钟应用于两个IC之间,用于数据发送以及接收,这种同步方式适用于长距离传输和低速传输,例如在通信系统中的数据传输。

- 自同步指 IC之间通信时,发送IC生成包含数据和时钟的流,发送至接收IC

DDR为源同步方式,传输数据的同时需传送与数据同步的时钟,一个时钟周期传递 2 个data,且上升沿对准data的中部,接收端使用该时钟对接收的数据进行处理。

2、数据读写

1、层级架构

综上,DDR读写层级架构可以概括为:

2、基本过程

a、相关概念

- 核心频率:SDRAM 内部存储颗粒的时钟频率。n Prefetch 需要内部存储单元在核心频率下读n倍的数据

时钟频率:I/O Buffer的时钟频率,根据 n Prefetch,时钟频率是核心频率的 倍

倍

如下图所示为一颗 512M x 8 的DDR3颗粒内部框图,采取 64bit Burst传输,实现 8n Prefetch,此处 n 即I/O位宽,为 8bit,I/O buffer一次Burst传输 8 倍I/O位宽,即64bit

可以看出,DDR3 芯片内部的数据总线是其接口位宽的 8 倍,即内部数据总线是 64 位,一次行列选择操作能同时选中 64 个 Cell,驱动 64 个读写电路同时工作,完成 64位数据的读写。读出的 64 位数据被锁存在 8 个 8 位的 FIFO 缓冲队列中,靠 4 倍于内核时钟的高速接口时钟,分 8 个上升下降沿传输完成

b、读写命令

- ACT_n:定位到 Row

RAS(Row Address Strobe)通过行地址定位,把 Bank 中一整行的数据都加载到此 Bank 的 Sensee Amp中 - CAS_n:定位到 Column

CAS(Column Access Strore) 从刚加载到 Sense Amp 中的一行数据中,选取出一列数据

DDR controller 发出一个 ACT 信号(CS_n 定位 Rank,BA 定位 Bank,Address 定位行、列),对应的 Bank 上的 Sense Amp 便加载对应行的数据,即把 Page 打开,然后按照 Burst 顺序,将连续的列地址的数据进行连续地读出。

-

相关阅读:

深度学习入门(4) -Object Detection 目标检测

【信息安全原理】——IP及路由安全(学习笔记)

【家具建模三剑客】3DMAX一键生成软包插件BreadMaker面包机插件使用教程

bmp图片处理

vue瀑布流插件vue-waterfall-plugin

【微服务】微服务之Feign 与 Ribbon

Linux--MQTT(二)通信基本原理

json、jquery、ajax

SpringBoot如何使用JDBC操作数据库呢?

【洛谷 P1097】[NOIP2007 提高组] 统计数字 题解(向量+排序)

- 原文地址:https://blog.csdn.net/VampireWolf/article/details/132907081