-

Windows保护模式(七)2-9-9-12分页

与10-10-12分页的区别

相对于 10-10-12 分页,2-9-9-12分页增大了 PDE,PTE 等结构的长度,使其描述的地址范围更大(64G),并且增加了 PTPTT一级,使得页表内不需要存储 CR3 的值,增加安全性。

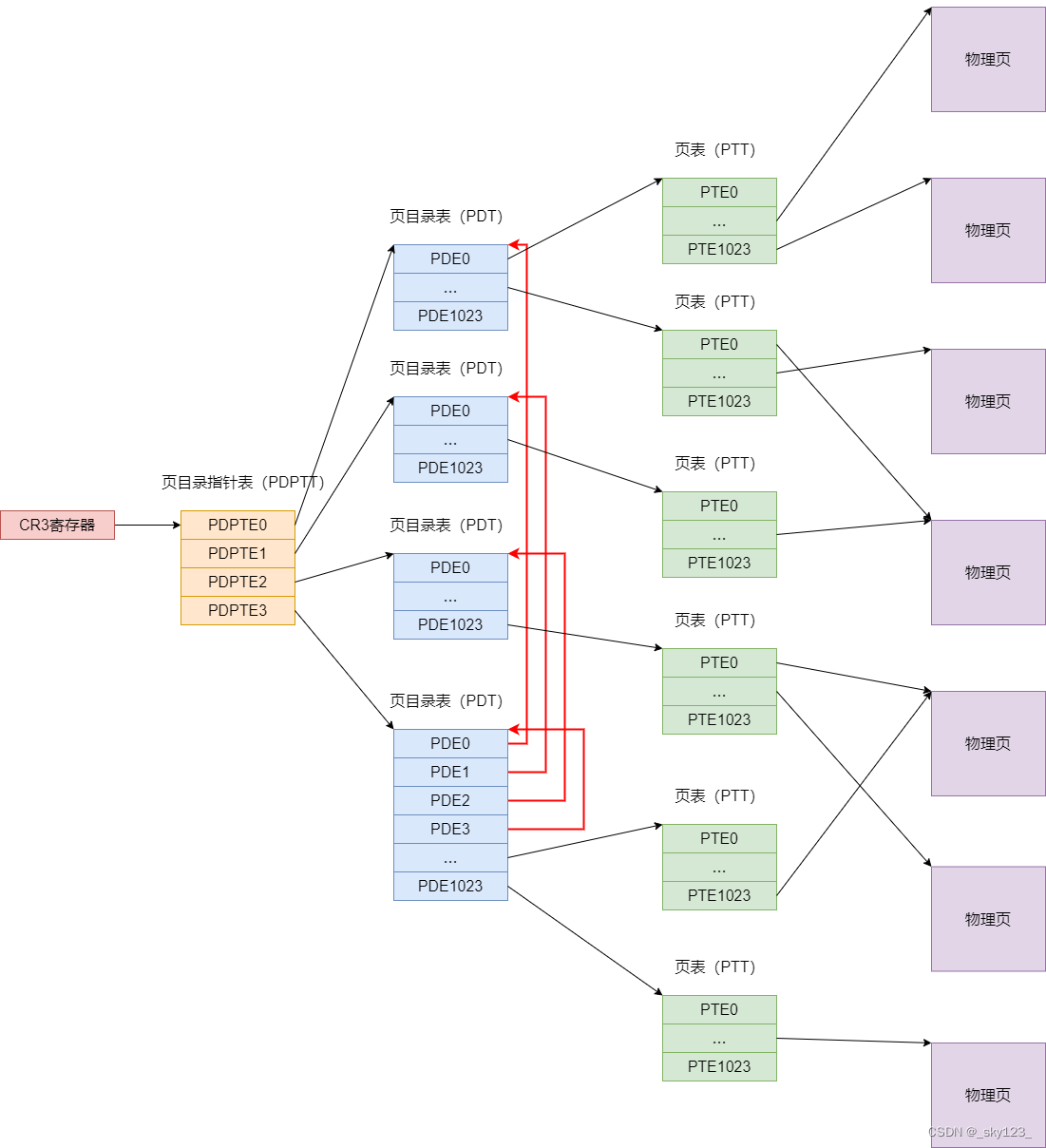

2-9-9-12分页结构

从 2-9-9-12 分页结构可以看出:由于没有指向 PDPTT 表基址的页表项,因此无法直接获取 CR3 寄存器的值。但依旧可以通过第 4 个 PDT 的特殊结构利用线性地址访问任意页表。

另外由于可访问的物理地址范围增大,因此 PDPTE,PDE,PTE 大小均扩大为 8B 。线性地址到物理地址转换过程

2-9-9-12 的线性地址到物理地址转换过程与 10-10-12 分页相似,只不过多了一层 PDPTE 。物理页属性

PDPTE

-

P位:第0位,有效位

-

Avail:这部分供操作系统软件随意使用,CPU不使用

-

Base Addr:指向PDT表地址,由两部分组成

- 第一部分:高四字节32~35位

- 第二部分:低4字节12~31位

这两部分加起来共24位,后12位补0

-

灰色部分:保留位

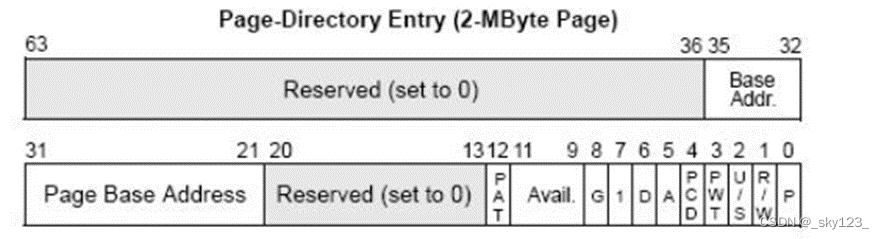

PDE

- PS 位:

- 当PS=1时是大页,35-21位是大页的物理地址,这样36位的物理地址的低21位为0,这就意味着页的大小为2MB,且都是2MB对齐。

- 当PS=0时,35-12位是页表基址,低12位补0,共36位。

PTE

- PTE中12~35位是物理页基址,低12位补0

- 物理页基址+12位页内偏移指向具体数据

XD/NX标志位

Intel中称为XD,AMD中称为NX,即No Excetion。

段的属性有可读、可写和可执行;页的属性有可读、可写。当RET执行返回的时候,如果把堆栈里面的数据指向一段提前准备好的数据,那么就会产生任意代码执行的后果。所以,Intel就在这方面做了硬件保护,设置了一个不可执行位 – XD/NX位。

当XD=1时,软件产生了溢出也没有关系,即使EIP蹦到了危险的“数据区”,也是不可以执行的。在PAE分页模式下,PDE与PTE的最高位为XD/NX位。

-

-

相关阅读:

自定义结构体的json序列化

js Fetch返回数据res.json()报错问题

GPT润色指令

基于springboot实现流浪动物救助网站系统项目【项目源码+论文说明】计算机毕业设计

配置类信息赋值为Java静态变量「扩展点实战系列》」- 第441篇

【我不是熟悉的javascript】使用postMessage+iframe实现授权登录

Android kotlin 实现一键清理内存功能

【Java企业级项目】数字货币交易项目

想成为优秀的HR,从哪些方面努力?

python LeetCode 刷题记录 104

- 原文地址:https://blog.csdn.net/qq_45323960/article/details/127414045