-

【小月电子】FPGA开发板(XLOGIC_V1)系统学习教程-LESSON10

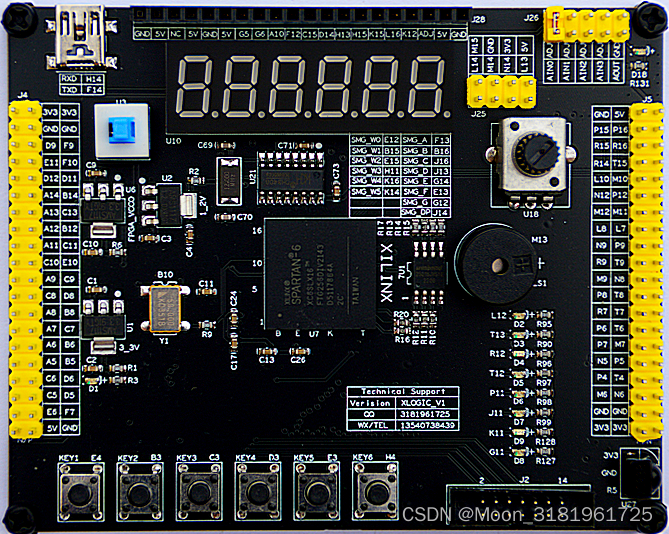

无源蜂鸣器驱动实验例程讲解 若要观看该博客配套的视频教程,可点击此链接 开发板实物图

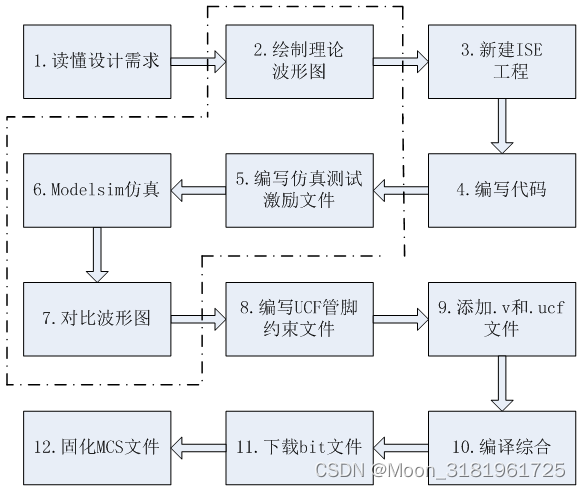

根据多年工作经验,总结出的FPGA的设计流程,概括起来总共有以上12步,其中根据项目难易度可省去其中一些步骤。比如非常简单的项目,我们可以省去虚线框里面的步骤,但是我们的入门级课程,即使再简单,也按照这12个步骤来进行讲解。1. 需求解读

1.1 需求

按下KEY2蜂鸣器报警,松开KEY2关闭报警

1.2 知识背景

蜂鸣器是一种一体化结构的电子讯响器,因其体积小、重量轻、价格低、结构牢靠而广泛应用于报警器、电子玩具、汽车电子设备、电话机、定时器等电子产品中作发声器件。本章节将详细介绍如何使用按键去控制蜂鸣器发声。

1 蜂鸣器简介

蜂鸣器按其结构可分为电磁式蜂鸣器和压电式蜂鸣器两种类型。电磁式蜂鸣器由振荡器、电磁线圈、磁铁、振动膜片及外壳组成。压电式蜂鸣器主要由多谐振荡器、压电蜂鸣片、阻抗匹配器以及共鸣箱、外壳等组成。压电式蜂鸣器是以压电陶瓷的压电效应,来带动金属片的振动而发声;而电磁式蜂鸣器则是用电磁的原理,通电时将金属振动膜吸下,不通电时以振动膜的弹力弹回。由于两种蜂鸣器发声原理不同,电压式结构简单耐用但音调单一、音色差,适用于报警器等设备;而电磁式由于音色好,所以多用于语音、音乐等设备。蜂鸣器按其是否带有信号源又分为有源蜂鸣器和无源蜂鸣器。有源蜂鸣器的内部装有集成电路,不需要音频驱动电路,只需要接通直流电源就能直接发出声响。而无源蜂鸣器只有外加音频驱动信号才能发出声响。

有源蜂鸣器只能发出固定频率的声音,不适合用来做音乐播放器,为了让我们开发板功能更全面,我们选用无源蜂鸣器, 所以这里为大家介绍无源蜂鸣器的驱动方式。

2. 无源蜂鸣器驱动原理

无源蜂鸣器与有源蜂鸣器不同,因其内部不带震荡源,所以其无法向有源蜂鸣器那样直接用直流信号驱动,这里需要使用PWM方波才能驱动其发声。

如何发出不同的声音呢?上面说到需要使用PWM方波才能驱动其发声,所以这里我们只要控制输入的PWM方波,输入不同频率和占空比的PWM方波发出的声音就不一样了。而不同频率和占空比的方波发出的声音是不同的,其中频率对音调有影响,占空比对音量大小有影响。所以我们只需产生不同频率和占空比的PWM方波去驱动无源蜂鸣器就能让无源蜂鸣器发出不同的音调了。

PWM的频率:是指1秒钟内信号从高电平到低电平再回到高电平的次数(一个周期);也就是 说一秒钟PWM有多少个周期。单位: Hz

PWM的周期与频率的关系:

T=1/f

周期=1/频率

50Hz = 20ms 一个周期如果频率为50Hz ,也就是说一个周期是20ms 那么一秒钟就有 50个PWM周期

占空比:是一个脉冲周期内,高电平的时间与整个周期时间的比例

单位: % (0%-100%)

表示方式:20%

上图中,周期为T

T1为高电平时间

T2 为低电平时间假设周期T为 1s ,那么频率就是 1Hz ,高电平时间0.5s ,低电平时间0.5s, 总的占空比(T1/T)就是 0.5 /1 =50%

1.3 硬件设计

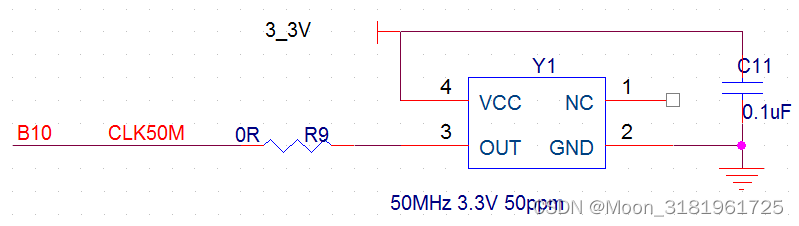

图5.有源晶振

1.4 接口说明

信号名 方向 FPGA管脚号 说明 CLK50M 输入 B10 时钟信号,50MHZ KEY1 输入 E4 按下为低电平,松开为高电平,作为复位信号 KEY2 输入 B3 按下为低电平,松开为高电平,作为蜂鸣器控制信号 BEEP 输出 F14 PWM方波,用于驱动无源蜂鸣器 总结:通过上述说明,可以将需求解读成:按下KEY2,M13管脚输出一定频率的PWM信号,蜂鸣器发声; 松开按键,M13管脚置为高电平,蜂鸣器停止发声

2. 绘制理论波形图

程序框图

无源蜂鸣器驱动理论波形图 * 通过上图,大家能算出方波(beep)的频率吗?假设时钟clk为50Mhz(周期20ns)一个beep信号周期有2x(pwm_num+1)个clk周期(有同学会问,为什么是pwm_num+1个周期呢?那是因为是从0开始计算的)。所以,beep的周期等于2x(pwm_num+1)20(单位ns),换算成秒等于2x(pwm_num+1)x20/1000/1000/1000,所以频率等于1/(2x( pwm_num +1)x20/1000/1000/1000)单位HZ。假如pwm_num=1000,那么频率等于24975HZ。

3.新建ISE工程

为了让工程看起来整洁,同时方便工程移植。我们新建4个文件夹,分别是Project,Source,Sim,Doc。

Project — 工程文件夹,里面放的ISE工程

Source — 源代码文件夹,里面放的工程源码(.v文件或.vhd文件)

Sim — 仿真文件夹,里面放的仿真相关的文件

Doc — 存放相关资料,比如数据手册,需求文档等4.编写代码

/// //QQ:3181961725 //TEL/WX:13540738439 //工程量:Mr Wang //模块介绍:产生一定频率的方波(PWM波)驱动无源蜂鸣器 /// module alarm_ctrl( input clk , input rst_n , input key , output beep ); parameter pwm_num=20000; reg [15:0] cnt=0; reg beep_tmp;//PWM信号 assign beep=(key==0)?beep_tmp:1'b1; always@(posedge clk or negedge rst_n)begin if(!rst_n) cnt<=0; else if(cnt==pwm_num) cnt<=0; else cnt<=cnt+1; end always@(posedge clk or negedge rst_n)begin if(!rst_n) beep_tmp<=0; else if(cnt==0) beep_tmp<=~beep_tmp; else; end endmodule- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

5.编写仿真测试激励文件

仿真框图 仿真测试激励文件(TB文件)

`timescale 1ns/1ps module alarm_ctrl_tb; reg clk; reg rst_n; reg key; initial begin clk=0; key=1;//按键未按下 rst_n=0;//生成复位激励信号 #1000 rst_n=1;//生成复位激励信号 #1000000 key=0; end //生成时钟激励信号 always #10 clk<=~clk; //例化被仿真模块 alarm_ctrl Ualarm_ctrl( .clk (clk), .rst_n (rst_n), .key (key), .beep () ); endmodule- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

6.Modelsim仿真

Modelsim仿真一般有两种方法

-

图形化界面仿真,即所有的操作都是在Modelsim软件界面上来完成,该方式的优点是,简单易学,适用于简单的项目,缺点是操作步骤繁琐。

-

批处理仿真,这种方式在仿真前需要编写相应的脚本文件,该方式的优点是,一键即可完成仿真,省时省力,缺点是前期需要编写脚本文件。前两讲采用的是图形化界面仿真的方式;为了更贴近工程实际,从第三讲开始,我们就采用批处理方式仿真。具体操作步骤可参考我们的视频教程

仿真出的波形如下图所示:

7.对比波形图

将第二步绘制的理论波形图与第六步Modelsim仿真出来的波形图进行对比,结果一致,说明我们的逻辑设计是正确的。如果发现比对结果不一致,就需要找到不一致的原因,最终要保证对比结果一致。通过对比,理论波形与仿真波形一致,说明功能符合设计要求。

8.绑定管脚(编写UCF文件)

NET "clk" TNM_NET = "clk"; TIMESPEC TS_sys_clk_i = PERIOD "clk" 20 ns HIGH 50 %; NET "clk" LOC = B10 | IOSTANDARD = LVCMOS33 ; NET "rst_n" LOC = E4 | IOSTANDARD = LVCMOS33; NET "key" LOC = B3 | IOSTANDARD = LVCMOS33; NET "beep" LOC = M13 | IOSTANDARD = LVCMOS33;- 1

- 2

- 3

- 4

- 5

- 6

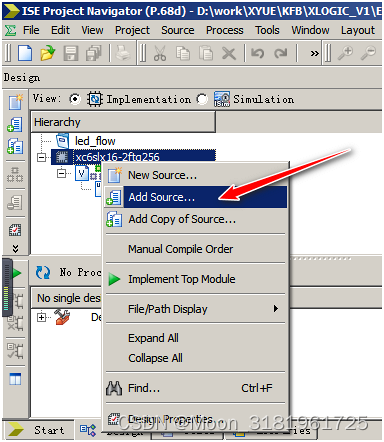

9.添加.v和.ucf文件

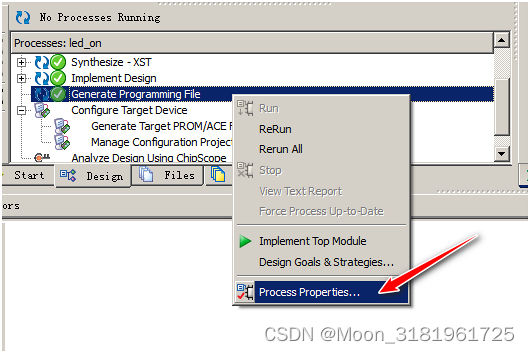

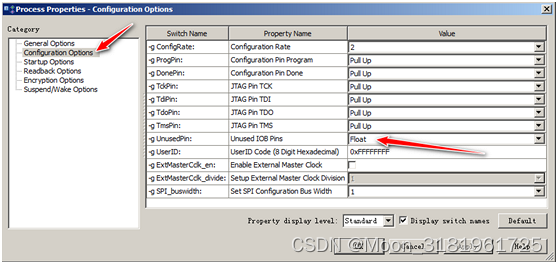

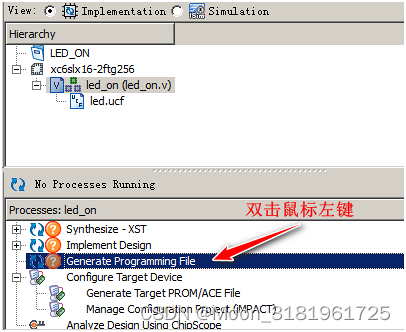

10.编译综合,同时将未使用管脚设置为悬空状态

1.设置未使用管脚为悬空状态

2.编译综合

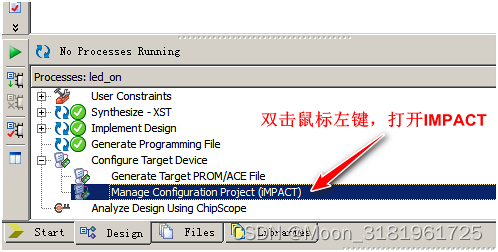

11.下载BIT文件

编译综合成功后便可以将生成的BIT文件下载到开发板(记得插上下载器,同时开发板上电)

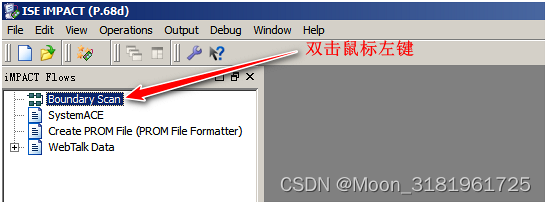

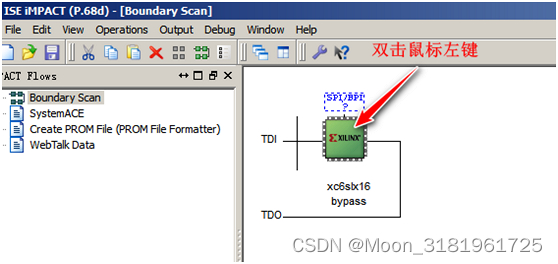

1.打开IMPACT

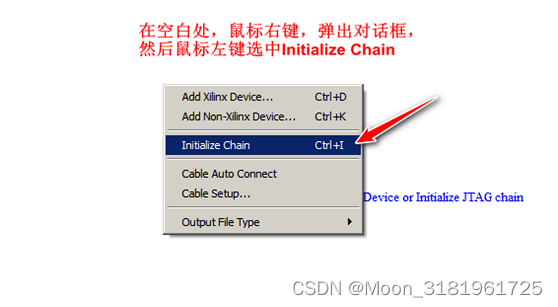

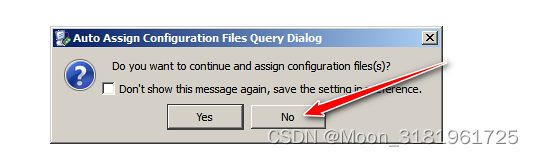

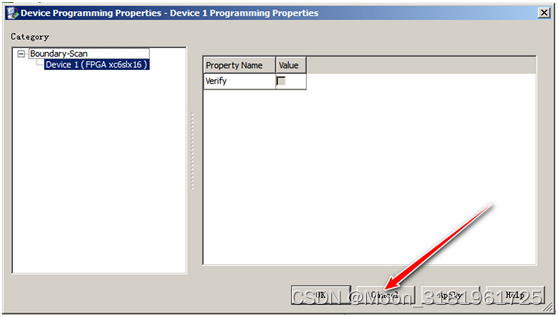

2.搜索器件

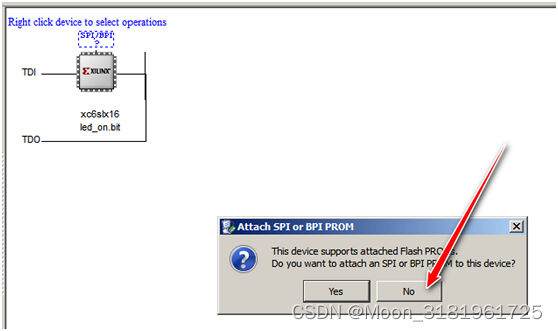

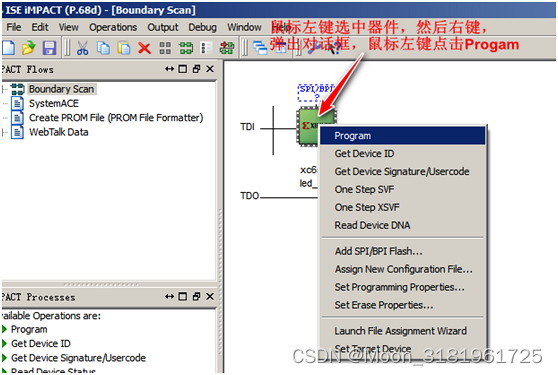

3.选择bit文件

下载成功后,便可以观察到开发板上的实验现象,如果实验现象与设计需求相符,那说明我们的设计是没有问题的,即可进行下一步生成MCS文件

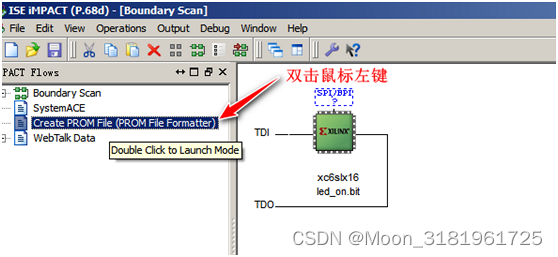

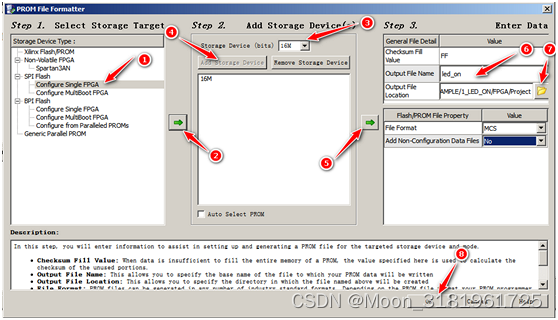

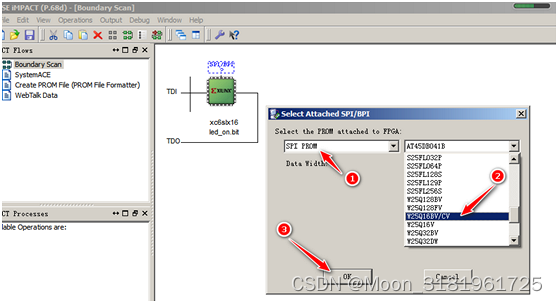

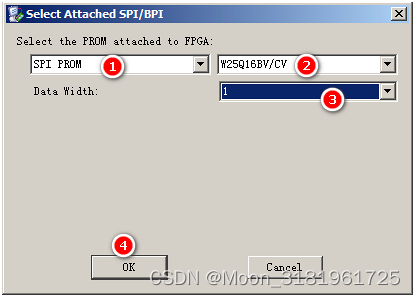

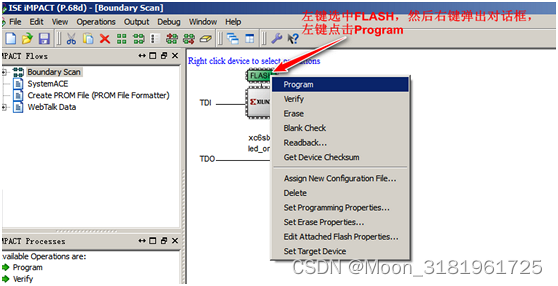

12.生成MCS文件,同时固化到配置芯片中

FPGA有一个特性,就是掉电后配置信息会丢失,所以我们需要将配置信息存储在配置芯片(FLASH)中,待开发板上电后,FPGA便会读取配置芯片中的配置信息,这样开发板掉电再上电后同样可正常工作。要将程序固化到配置芯片,需要先生成MCS文件。

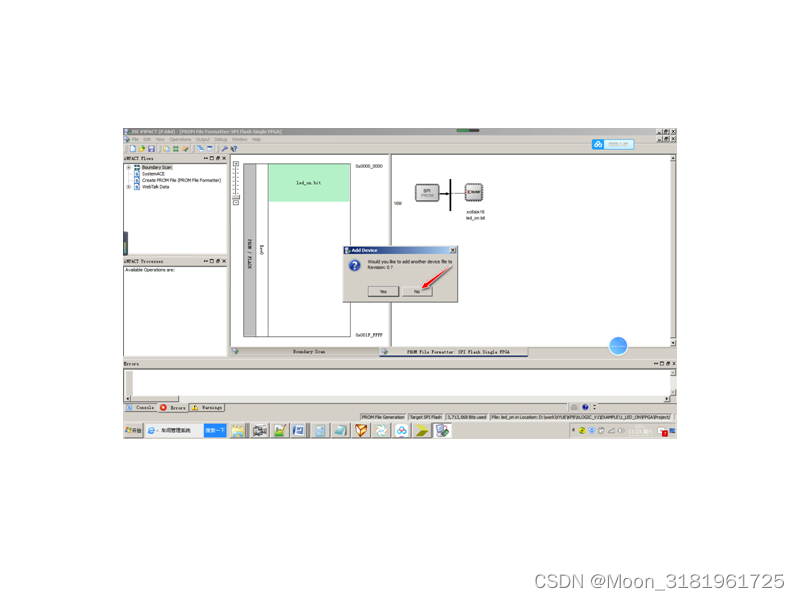

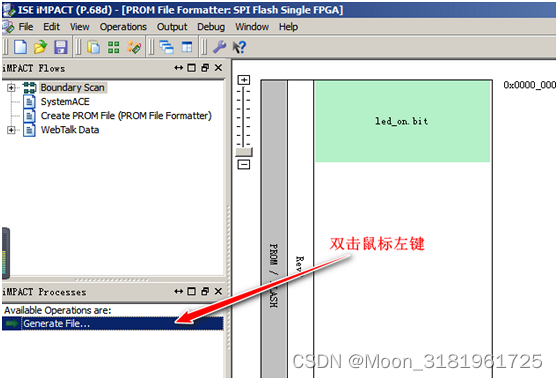

BIT文件转换成MCS文件步骤:

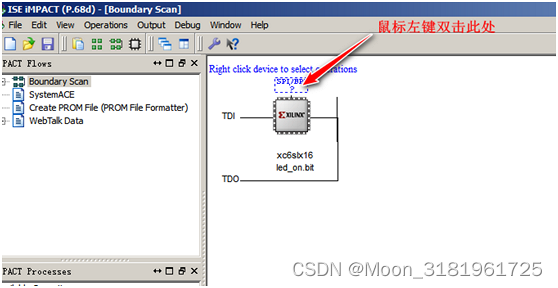

固化MCS文件

固化成功后,开发板断电再重新上电,可以观察到开发板仍然可以执行刚刚的功能。 -

相关阅读:

redis分布式锁的应用

Qt+windows开发备忘录

vscode 阅读 android以及kernel 源码

容错限流框架之Hystrix上

《Linux》day4--shell语法(下)

PostPreSql 数据库的一些用法

Maven下载与文件配置

第六章-Python数据可视化--2

Apache HTTPD 多后缀名解析漏洞复现

R语言ggplot2可视化:使用patchwork包将多个ggplot2可视化结果组合起来、两个可视化图像纵向组合之后再和另外一个可视化结果横向组合

- 原文地址:https://blog.csdn.net/Moon_3181961725/article/details/126720720