-

MTK SOC timing

目录

1、SOC timing – Scaler基本流程

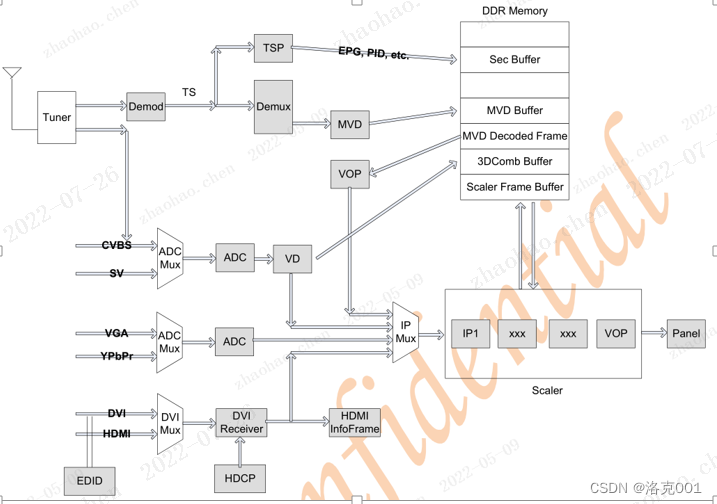

1.1 MTK的架构流程图如下

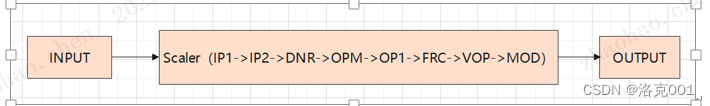

可以缩减为如下

如上图所示,每个源都会经过 Scaler 处理,最后 Scaler 输出到 Panel。Source 在经过 Scaler之前,也有其他模块处理的,在理清问题时也要考虑一下其他模式是否会出问题。

各个suorce简化流程:

ATV:Tuner->ADC->VD->IPMUX->Scaler

DTV:Tuner->Demod->Decode->MVOP->IPMUX->Scaler

HDMI:Hdmi Engine->IPMUX->Scaler

MM:Decode->MVOP->IPMUX->Scaler

CVBS:ADC->VD->IPMUX->Scaler

VGA:ADC->IPMUX->Scaler

YPBPR: ADC->IPMUX->Scaler对于 Scaler 来说上图可以简化为下图:

IPMUX:切 source 的选择开关

IP1:sync detect,color space 转换

IP2:h/v prescaling down,注意只能 down,不能 up

DNR:写 memory,相关 PQ 图效操作

OPM:读 memory,相关 PQ 图效操作

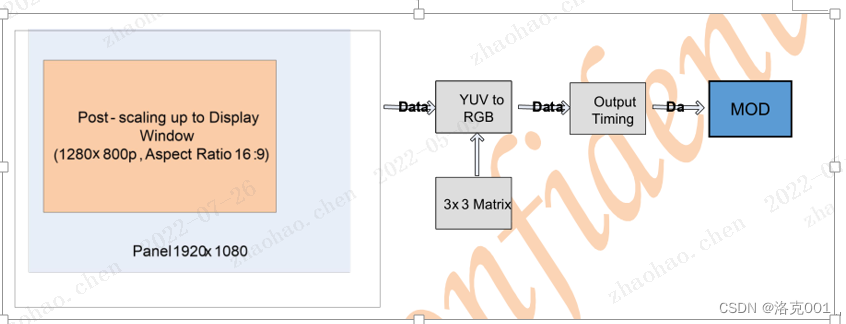

OP1:post scaling

FRC: MEMC 倍频

VOP:display window,color matrix

MOD:屏端设定

1.2 IP1

Scaler 的 IP1 可以反馈前端送进来的信号,主要是

Input Timing width&height

Input Timing interlace or not

Input Vtotal,Input Vfreq,Input HFreq,Input Hperoid,Input Source 是否有打开。

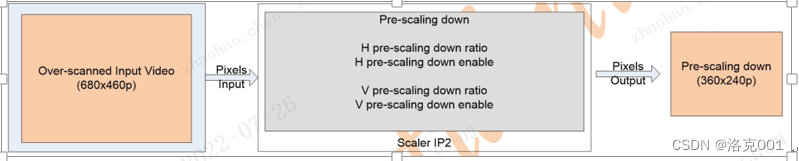

1.3 IP2

IP2 的功能是缩放,而且只能缩小不能放大。系统 BW 不够时或者小画面显示时,需要

IP2 做缩放。另外缩放系数是有限制的,不同的 chip 会不一样。

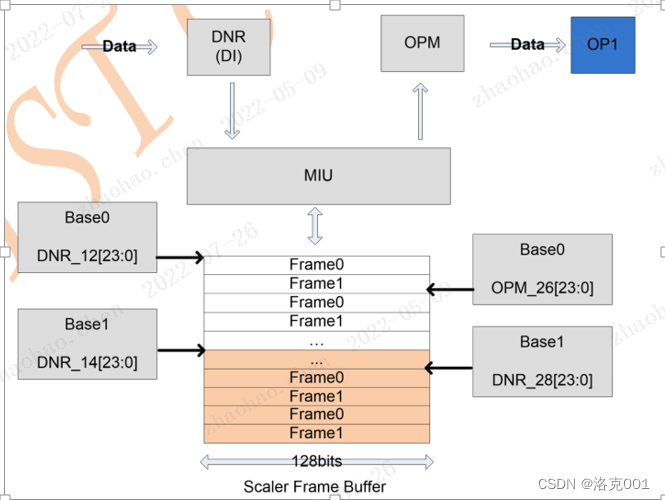

1.4 DNR/OPM

DNR 是把数据写进 DRAM 里面,OPM 是把数据从 DRAM 里面读出来,然后输出给 OP1。存多少张 Frame 是和系统还有 XC 的功能有关,流程图如下:

1.5 OP1

OP1 的功能也是缩放,不过主要是放大,缩小的能力比不上 IP1。放大也是有限制的,

至少不能超过 panel 的范围.

1.6 VOP

VOP 是设定输出的 timing,给到 panel。

-

相关阅读:

UI自动化测试、接口测试等自动化测试

echarts+vue实现柱状图分页显示

CSS3盒子模型

聊聊Excel解析:如何处理百万行EXCEL文件

【Java】反射 之 获取继承关系

学生选修课程管理系统c++

由山东高考今日出分记

指令的类型

数据结构——顺序表和链表

LeetCode 210:课程表 II (拓扑排序)

- 原文地址:https://blog.csdn.net/niaohaoge/article/details/126001644