-

计算机组成原理第三章 13 主存芯片的构成 主存和CPU之间的连接 字扩展和位扩展 $\color{red}{2^n}$

主存储器存储芯片的构成 单个存储器芯片和CPU的连接

首先我们需要知道主存储器由多个存储芯片构成,每个存储芯片内含有多个存储单元,而主存使用的芯片一般是DRAM,我们下面介绍的就是DRAM,但是现在的主存一般是使用SDRAM了。

在计算机中存储的都是高低电平的电信号,通过高电平代表1,低电平代表0。接下来我们看看一个存储芯片是如何存储这些二进制高低电平信息的:存储芯片是通过存储元来存储高低电平信息的,一个存储元可以存储一个二进制信息。

( 1 ) (1) (1)存储元

一个存储芯片中包含了很多的存储单元,一个存储单元由多个存储元构成,一个存储元对应可以存储一位的二进制0或者1信号。

简单来看,存储元由这两个部件构成:

1.MOS管

2.一个下极板接地的电容电容:在高中物理我们就有接触过电容这一元器件,电容由上极板,下极板和夹在中间的介质组成。对于电容这一元器件来说,当上下极板产生电压差以后,电荷就会在电容中产生流动,可以起到对电容进行充电的作用。在计算机中,电容内含有电荷表示二进制的1信号,不含有电荷则表示二进制的0信号。

MOS管:MOS管是一个半导体元器件,MOS管有一定的导通电压,只有当电压达到导通电压以后,MOS管才会导通,才能通过电流。如果没有达到导通电压,MOS管就是断开的,无法通过电流。

注:MOS管是一个半导体元器件,半导体的意思就是半导通,半绝缘,MOS管高电平时导通,低电平时绝缘。

存储元是如何存储二进制的信息的?

如何存储二进制的1信号?

1.给MOS管一个导通电压,使其导通以后能够通过电流

2.输入一定的电压,电荷随着导线流动到电容的上极板,上下极板产生电压差,电容内电荷流动,对电容起到充电作用。

3.电容充电完毕以后将MOS管断开,这样电荷就保存在电容中了。如何存二进制的0信号?

不做任何操作,电容内不存储电荷就是代表二进制的0信号。

如何读取存储元中的二进制01信号?

给MOS管一个导通电压,使其导通,电容内的电荷会随着导线流出。在电流的出口处进行检测:

1.检测到电流,说明为二进制的1。

2.没有检测到电流,说明为二进制的0。

在明白了存储元以后我们看下存储单元是如何设计的:

一个存储单元就是由多个MOS管组成,一个存储单元的内容MOS管被一根导线串联在一起,所以只要红色的这跟导线发送一个高电平信号,处于一个存储单元的MOS管就都会被导通,加上每个MOS管都连接了数据总线,这样我们一次就可以读出一个存储单元的数据,这也是为什么我们之前说每次读取的基本单位是一个存储单元。

在明白了存储单元的设计以后,我们开始融入其他的部件:

事实上一个完整的存储器芯片是如下的(不包括MDR和MAR)。

对此我们进行一一的介绍:

在这个图中,具有两个译码器蓝色的那个译码器位于CPU和主存之间,其不在主存内,其用于翻译CPU发送的片选信号,然后翻译以后导通对应的片选线,因为片选线连接了CPU内的译码器,所以CPU可以使用片选线来决定是否需要让译码器进行工作,即让存储芯片进行工作。CPU传输给蓝色译码器的信号可能是使用地址线充当的,不一定是控制线。所以对于蓝色的译码器和主存内的译码器,我们分别说明其作用:

主存内的译码器::翻译MAR传输的地址,并给对应存储单元的字选线一个高电平信号,n位的MAR就有n条地址线,有 2 n \color{red}{2^n} 2n个地址,即这么多个存储单元,对应就有 2 n \color{red}{2^n} 2n条字选线,每个字选线对应一个存储单元,所以我们想要读某个存储单元的数据的时候,只要给对应存储单元的字选线一个高电平信号即可。

蓝色的译码器:

蓝色的译码器类型比较多,我们进行解释:

首先我们需要知道,这里的G1,G2A和G2B一般是CU的控制总线,左边红色的用于控制片选信号的一般是使用的地址总线。这里的控制总线我们暂时先忽略。和主存内的译码器类似,在主存的译码器中,我们左边对应的是地址总线,右边对应的是字选线。而在CPU外的译码器中,我们左边同样也是地址总线,但是右边是连接了多个存储芯片的片选线。例如我们下图中有3条地址线,那么右边就对应有8条片选线。我们知道一个存储器内有多个存储器芯片,每个存储器芯片对应有一个片选线,所以下图中就可以连接8个存储器芯片,然后译码器根据左边地址总线的输入端,判断需要导通哪根片选线。例如下图我们输入的是101,对应十进制是5,所以译码器就会导通第5根片选线,就可以让连接5号片选线的存储芯片内的译码器进行工作,即存储芯片进行工作。

注:控制线上带有-表示低电平有效,不带-表示高电平有效,一般来说如果是低电平有效的,就需要画-,并且需要在外面画一个圆圈,例如上图中G2就是低电平有效,具有一个圆圈和一个横线。现在我们就来说下译码器中三条控制总线的作用:其中G1和G2A一般会被直接导通,而G2B一般会等下才导通,G2一般连接着CPU的MREQ,MREQ叫做主存访问信号,只有CPU发送这个信号给G2以后,译码器才会开始工作。

关于为什么需要发送MREQ信号接下来我们通过一个完整的工作过程进行解释。

并且,我们需要知道,发送片选信号的译码器和主存的使能信号是需要进行搭配使用的,如图所示:

对于主存储器的工作过程,还具有很多细节我们一一进行介绍:

工作过程:

CPU将地址信号转发给MAR,但是因为电信号具有不稳定的特点,所以CPU暂时不会发送MREQ访存信号给片选译码器,等待MAR内的地址稳定以后,CPU会将MAR内的地址通过地址总线送至主存内的译码器,主存内的译码这时候还无法进行工作,其需要等待片选译码器的片选信号,接着CPU会通过控制总线发送MREQ访存信号给片选译码器,片选译码器经过翻译以后会给对应的片选线发送一个信号,对应的存储器芯片在收到片选信号以后,译码器会开始工作,译码器对收到的地址进行翻译,翻译以后的地址会发送给旁边的驱动器进行信号放大,然后驱动器导通对应的选通线,最后数据从数据总线流至MDR,当数据到了MDR内部的时候,同样是因为电信号具有不稳定的特点,所以CPU会等待MDR内的电信号稳定以后才将数据转换给CPU内的其他部件。这里需要补充一下,一般来说一整个主存只有一共译码器,所有的存储器芯片共用这个译码器。我们可以这样理解:这个字选译码器在n位地址的情况下和每个芯片都有 2 n \color{red}{2^n} 2n条字选。然后当片选译码器导通一个芯片以后,这个芯片会给译码器一个反馈,译码器就知道哪个芯片被导通了。接下来就知道需要导通哪个芯片的子选线了。

现在我们开始了解片选线,读写控制线的作用:

我们知道一个存储器有多个存储芯片组成,我们每次访存的时候只需要读取其中一个存储器芯片,所以片选线就是存储器的"开关",片选线是每个存储器芯片都有一个,这个片选线通过控制总线和CPU内的CU连接在一起,所以CU想要某个存储器芯片工作的时候只需要发送给片选线一个低电平信号(片选线一般是低电平有效,具体看题目),给其他的存储器芯片发送一个高电平信号即可。

写控制线:当CPU想要往一个存储器芯片写入数据的时候,其就会发送一个信号给控制电路

读控制线:当CPU想要往一个存储器芯片读出数据的时候,其就会发送一个信号给控制电路

当然读写控制线也有可能是合在一条的,这时低电平信号就是写,高电平信号就是读。注意:在外部看来片选线,读写控制线,数据线,地址线就是一个个金属引脚。除此之外还有供电引脚,接地引脚。

所以我们最终可以对存储器芯片的模型进行抽象化:

位扩展

位扩展扩展的是什么?

通过扩展存储器芯片来达到存储单元大小的扩展,但是不会扩展地址线的条数。

位扩展的本质就是:通过同时使用多块存储器芯片,达到扩充主存的存储字长

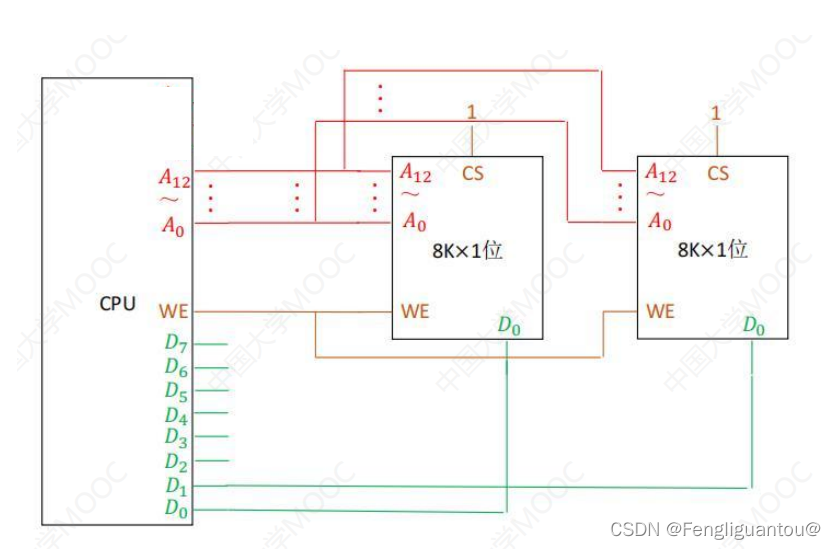

例如下图:

在下图中我们可以看出,cpu和单块的存储器芯片进行了连接,CPU中具有8条数据总线,存储单元的存储字长为1。这时候CPU只让一块存储器芯片进行工作,所以这时候CPU每次只能从存储器芯片内获得一位的信息,即每次传输只需要使用一条数据总线,但是CPU中具有8条数据总线,这样就会导致数据总线的浪费。

所以我们可以进行连接:

我们通过cpu的地址总线将两块存储器芯片连接在了一起,所以每次CPU会送来一个地址,将这个地址送往两个存储芯片,因为用的是相同的地址线,所以两个存储芯片会取出相同位置的数据,然后选择不同的数据总线传输给CPU。

如果我们通过这样的方式将8个存储器芯片进行连接,就能够完全利用CPU的数据总线了,这就是所谓的位扩展。在位扩展中,存储器芯片使用相同的地址总线,片选线,读写控制线。但是使用的数据总线是不同的。可以这里理解:可以理解为进行位扩展以后,存储器芯片就可以看作是一块了。假设是4个存储器芯片进行位扩展,那么一次就能读出4个相同地址的存储单元。因为位扩展本质也就是将两个芯片合成一个芯片组。

字扩展

字扩展扩展的是什么?

通过扩展存储器芯片的数量,从而扩展存储单元的个数。字扩展,也就是增加存储器芯片的个数,增大寻址范围。说白了就是CPU选择导通哪一个存储器芯片

前面我们说过每个存储器芯片都有一个片选信号,当接收到片选信号的时候,存储器芯片才能开始工作,在计算机中片选信号是CPU发送的,实际上CPU是通过地址总线来发送片选信号的,其中片选信号的发送方式具有两种,分别是线选法和片选法。

( 1 ) (1) (1)线选法

优点:不需要片选地址译码器,线路简单。

缺点:地址空间不连续,不能充分利用存储器的空间。(对此应该这样理解:第一,体号地址不连续导致CPU寻址不连续,第二因为每个存储器芯片/芯片组都需要单独一条片选线,但是片选线本质上使用的是CPU的地址线,所以可能导致一个问题,即存储器芯片组有多个,片选线不够用,所以造成地址资源的浪费。)注:线选法的片选线默认是使用高位的地址线。

假设在下图中有两个独立的芯片组,其中两个芯片组分别连接了两条地址总线作为片选信号,由于CPU每次只能让一个芯片组进行工作,所以两条地址总线只能具有两种有效的组合:即01或者10,只有这两种方式才能只让一块芯片进行工作

如何深入理解地址不连续?

进行访存的时候,我们给一个地址。其中假设四个存储器芯片,在线选法下,前4位就代表选择哪一个存储器芯片。例如1000表示第一个。这样对于编程而言会出现问题,即如果想要访问1100…实际上是没有这个存储器芯片的。

( 2 ) (2) (2)译码片选法

译码片选法:使用地址总线连接译码器,地址总线将片选信号发送给译码器,译码器对其进行翻译,然后导通对应芯片组的片选线。

优点:n条地址线可以控制 2 n \color{red}{2^n} 2n个芯片组的片选信号。并且因为体号中所有组合都是有效的,所以地址是连续的。译码片选法默认使用高位的地址总线来作为片选线。

片选线的条数说明了什么?

片选线的条数说明了芯片组的个数,说明了有多少个芯片组。

优化思路:

在多余的地址线传输过程中加上一个非门,也就是这里的1-2译码器,所以一条地址线就可以对应发出两个片选信号。

在这个基础上继续优化,3-8译码器的出现,3-8译码器似乎会复杂一点,3条地址线可以对应8种状态,所以可以通过这种优化思路以后,主存内的地址就是连续的了,例如00开头的地址对应第一个存储器芯片,01对应第二块存储器芯片,接着是10,11。CPU可以搭配片选信号选择使用的存储器芯片。

下图需要注意的是,第二块存储器芯片和后面的存储器芯片的地址并不是从第一块存储器芯片转发来的,而是从连接第一块存储器芯片的地址总线传递来的,为了不让图片很乱,所以下图就没有这样画。

需要非常注意,不同的存储器芯片,即使用不同片选信号的存储器芯片,其一定是使用不同的读写控制电路,这很好理解,如果是相同的读写控制电路,那如何控制多块不同的芯片写入。⭐⭐⭐⭐⭐⭐

需要注意的是,在题目中,可能会出这种脑瘫的连接方式:

即连接片选译码器的地址线不是连续的,中间空了一条。

这种接法会导致一个问题:我们看第一个芯片A,,其正常地址范围是12个0到12个1,即

2 1 2 \color{red}{2^12} 212 个地址,但是如果中间缺了一条线,就会导致出现 2 1 3 \color{red}{2^13} 213个地址,这明显是具有问题的。 但是这个其实不影响寻址。这个就是个nt玩意。

注意:字扩展是将不同存储器芯片的地址总线,数据线,读写控制线共用,但是片选线不共用,并且字扩展就是类似高位交叉编址和低位交叉编址,可以这样记忆,但是记住其不是高位交叉编址和低位交叉编址,只要记住有体号即可。需要非常注意的是,题目中的片选译码器可能不是一个3-8译码器之类的译码器,题目可能给了实际的电路,然后给了片选地址,让你分析这个片选地址是否合理:我们判断片选是否合理就是看片选经过电路以后,产生的0或者1信号是否能够导通一个芯片组,因为如果我们这个片选地址没法导通任何一个芯片,那就说明这个地址无效的,所以这类题目我们一般是通过电路然后根据片选地址判断出译码器得到的片选信号和芯片需要的片选信号是否相同。

例如下面的这题:字位同时扩展

两个特征:

位扩展的存储器共用一个片选信号。

字扩展不同的存储器芯片共用数据总线和地址总线。字扩展和位扩展中地址线,数据线,读写控制线,片选线的共用

( 1 ) (1) (1)字扩展

同用地址线,读写控制线,片选线。

( 2 ) (2) (2)位扩展

同用地址线,数据总线,读写控制线(这里应该理解为因为每次访存只需要一块存储器芯片工作,所以可以大家共用,因为其他的存储器芯片接收到读写信号也没关系,其片选信号没有被导通是无法工作的。)

字扩展和交叉编址的区别

首先需要知道,字扩展和交叉编址是具有区别的。

( 1 ) (1) (1)片选线的选择

字扩展中无论是线选法还是译码器片选法都是使用的高位地址总线。

而在交叉编址中,既有使用高位,也有使用低位。( 2 ) (2) (2)译码器

字扩展中一个存储器芯片一个译码器。

交叉编址中译码工作一般是交付给第一个存储器芯片或者最后一个存储器芯片。存储器容量相除以后得到的结果

在存储器容量中 64 K × 8 \color{red}{64K \times 8} 64K×8意思是有64K个存储单元,每个存储单元是8bit。存储单元的个数说明了地址线的条数, 地址线的位数。

存储器容量相除:例如 64 K × 8 \color{red}{64K \times 8} 64K×8 / 32 K × 4 \color{red}{32K \times 4} 32K×4相除得到的结果就是需要有多少块这样的芯片才能扩展成这样。其中8/4=2说明在 64 K × 4 \color{red}{64K \times 4} 64K×4 情况下每个芯片组需要两个存储器芯片,64K/32K=2,说明在 32 K × 8 \color{red}{32K \times 8} 32K×8的情况下,需要两个存储芯片组,根据存储芯片组可以推出片选的条数,所以最终可以得出需要2*2=4个芯片。所以如果题目问需要几个这样的存储器芯片,可以直接使用存储器容量进行相除。

-

相关阅读:

PyTorch入门教学——torchvision中数据集的使用

同步云盘:理解云端数据的实时同步技术

网络应用的基本原理

产品经理就业喜报:念念不忘,必有回响

java毕业设计菜篮子系统mybatis+源码+调试部署+系统+数据库+lw

利用aop+反射拦截mybatisplus的insert方法补充公共属性

Redis基础类型ZSet增删改查(带Java库源码)

网络安全(黑客)自学

js 实现图片纵向拼接并下载

「接口测试入门课」打卡学习 day09:微服务接口:怎么用Mock解决混乱的调用关系

- 原文地址:https://blog.csdn.net/weixin_59112191/article/details/129463559