-

Verilog的奇技淫巧[更新中]

1.Verilog常用的数据选择语句vect[a +: b]或vect [a -: b]

vect为变量名字,a为起始位置,加号或者减号代表着升序或者降序,b是进行升序或者降序的宽度。

因此,vect[a +: b]等同于vect[a : a+b-1],vect [a -: b]等同于vect[a : a-b+1]

例如:

vect[7 +: 3]

其中,起始位置为7,+代表着升序,宽度为3。即从7开始往比7大的方向数3个数。其等价形式为:vect[7 +: 3]==vect[7 : 9]

vect[9 -: 4]

其中,起始位置为9,-代表着降序,宽度为4。即从9开始往比9小的方向数4个数。其等价形式为:vect[9 -: 4]==vect[9 : 6]

- 关于片选的一些补充

- 片选多个比特的正确语法有两种:

- assign out = in[sel*4 +: 4];// 从 sel*4 开始,选择比特序号大于sel*4 的 4 位比特,相当于[sel*4+3:sel*4]

- assign out = in[sel*4+3 -: 4]; // 从 sel*4+3 开始,选择比特序号小于 sel*4+3 的 4 位比特,相当于[sel*4+3:sel*4]

但是assign out = in[ sel*4+3 : sel*4 ],这个表达式不符合 Verilog 片选操作符的语法。2.integer变量不要放在for循环中,要提前定义integer变量。

3.重复次数必须是一个常量,而且请特别注意重复操作符有两对 { }.外层的 {} 不能少。

- wire [24:0]in0 = {{5{a}},{5{b}},{5{c}},{5{d}},{5{e}}};

- wire [24:0]in1 = {{5{a,b,c,d,e}}};

- //类似这种,花括号也不能少

4.模块信号连接的两种方式

一般都采用第二种,按端口名称连接模块信号

在实例化模块时,有两种常用的方式来进行模块端口的信号连接:按端口顺序以及按端口名称连接端口。

按端口顺序,

mod_a instance1 ( wa, wb, wc );wa, wb, wc 分别连接到模块的 第一个端口(in1),第二个端口(in2)以及第三个端口(out)。这里所谓的端口顺序指的是模块端口的定义顺序。这种方式的弊端在于,一旦端口列表发生改变,所有模块实例化中的端口连接都需要改变。按端口名称,

mod_a instance2 ( .out(wc), .in1(wa), .in2(wb) );在这种方式中根据端口名称指定外部信号的连接。这样一来就和端口声明的顺序完全没有关系。一旦模块出现改动,只要修改相应的部分即可。实际上,一般都使用这种方式来进行模块实例化。在instance的时候,尽量每个端口对应一行,例如:

- module top_module ( input a, input b, output out );

- mod_a U_mod_a(

- .in1(a)

- , .in2(b)

- , .out(out));

- //NVIDIA的开源代码就是这么写的

- endmodule

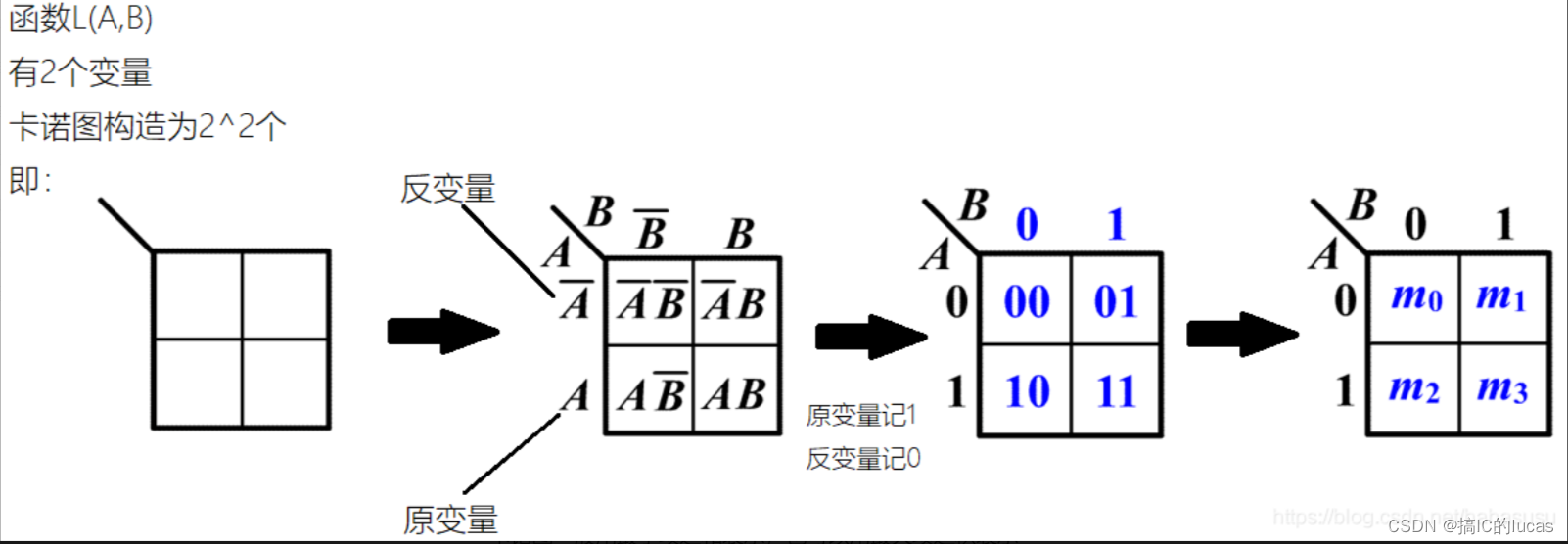

5.卡诺图化简

(1)最大项和最小项

- 最小项:n个变量的逻辑乘,即与形式,每个变量以原变量或者反变量的形式出现一次。n个变量共有2n个最小项。用m表示,如ABC,表示为m0。

- 最大项:n个变量的逻辑和,即或形式,每个变量以原变量或者反变量的形式出现一次。n个变量共有2n个最大项。用M表示,如A+B+C,表示为M0。

- 最小项的反是最大项,最大项的反是最小项。例如:~m0=~(~A&~B&~C)=A|B|C;

(2)卡诺图

- 在这个方格图中,每一个方格代表逻辑函数的一个最小项,而且几何相邻(在几何位置上,上下或左右相邻)的小方格具有逻辑相邻性,即两相邻小方格所代表的最小项只有一个变量取值不同。

- 卡诺图一般用最小项之和表示,也可以用最大项之积表示

例如

最小项表示:F = m1+m5

最大项就是:F = M0*M2*M3*M4*M6*M7

- 关于片选的一些补充

-

相关阅读:

VirtualBox(内有Centos 7 示例安装)

LeetCode - 解题笔记 -201- Bitwise AND of Numbers Range

Spring IoC 容器生命周期:Ioc容器启停过程发生了什么-13

集成RocketChat至现有的.Net项目中,为ChatGPT铺路

Qt添加自定义字体

26 JavaScript模块

LeetCode-409. Longest Palindrome [C++][Java]

MySQL故障排查与生产环境优化

Java面试之JavaWeb常用框架(offer 拿来吧你)

3D感知技术(4)双目立体视觉测距

- 原文地址:https://blog.csdn.net/qq_27148893/article/details/127107944