-

ads131a04 ADC verilog实现及仿真

ADS13104:datasheet

状态机图:

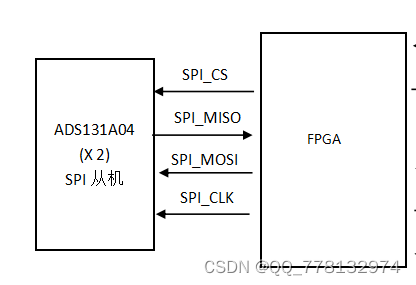

ADC与FPGA通信原理图:

FPGA 内部集成了一个 SPI MASTER控制器,负责和ADC芯片进行通信。

采样频率: 5120Hz 10240Hz ,ARM处理器可以通过SPI接口设定采样频率的高低。

在vivado上进行实现:

仿真截图:

verilog设计代码如下:

module ADC_MODULE(

input clk,//62.5ns

input rst_n,

output sclk,

output reg cs_n,

output reg mosi,

output reg[47:0] receive_data,

input miso,

output reg[7:0] bit_cnt,< -

相关阅读:

java 项目部署

CV&NLP基础9之卷积神经网络CNN入门

02-Tomcat打破双亲委派机制

Python开发工具

6.4 Web安全漏洞学习平台:WebGoat的使用

计算机网络——TCP/IP模型

Express 7 指南 - 开发中间件

计算机毕业设计ssm宠物托运网站8m8iz系统+程序+源码+lw+远程部署

mybatis学习(6):IntelliJ IDEA 如何创建一个普通的 Java 项目,及创建 Java 文件并运行

【1762】java校园单车投放系统Myeclipse开发mysql数据库web结构jsp编程servlet计算机网页项目

- 原文地址:https://blog.csdn.net/QQ_778132974/article/details/125528499