-

SOC项目AHB_SD_HOST控制器设计

目录

- 1.SD 2.0 协议

- 2.SD_HOST控制器设计架构

- 3.总线接口

- 4.SD_HOST寄存器介绍

- 4.1 CLK_EN_SPEED_UP_ADDR

- 4.2 SOFTWARE_RESET_REGISTER_ADDR

- 4.3 ARGUMENT_REGISTER_ADDR

- 4.4 COMMAND_REGISTER_ADDR

- 4.5 BLOCK_SIZE_REGISTER_ADDR

- 4.6 BLOCK_COUNT_REGISTER_ADDR

- 4.7 TRANSFER_MODE_REGISTER_ADDR

- 4.8 RESPONSE0_REGISTER_ADDR

- 4.9 RESPONSE1_REGISTER_ADDR

- 4.10 RESPONSE2_REGISTER_ADDR

- 4.11 RESPONSE3_REGISTER_ADDR

- 4.12 READ_TIMEOUT_CONTROL_REGISTER_ADDR

- 4.13 INTERRUPT_STATUS_REGISTER_ADDR

- 4.14 INTERRUPT_STATUS_MASK_REGISTER_ADDR

- 4.15 INT_GEN_REG_ADDR

- 4.16 CLR_INT_REG_ADDR

- 4.17 DMA_CTRL_ADDR

- 4.18 DAM_ADDR_ADDR

- 5.RTL代码

1.SD 2.0 协议

1.1 特性

- 标准容量SD存储卡:最大含2gb

- 高容量SD存储卡:大于2GB(此版本2.0规格限制容量不超过32GB)

- 电压范围:3.3v 工作电压范围:2.7- 3.6v

- 双电压SD存储卡:工作电压范围有低电压范围(T.B.D)和 2.7-3.6 V

- 有只读和读写两种模式

- 默认模式:可变时钟速率0 - 25MHz,高达12.5 Mb/s接口速度(使用4条并行数据线)

- 高速模式:可变时钟速率0 - 50MHz,高达25Mb/s的接口速度(使用4条并行数据线)

- 读取操作时拆卡不会损害内容

- 内容保护机制-符合SDMI标准的最高安全性

- 卡的密码保护(CMD42 - LOCK_UNLOCK)

- 使用机械开关的写保护功能内置

- 写保护功能(永久和临时)

- 卡检测(插入/删除)

- 特定于应用程序的命令

- 舒适的擦除机制

- 在SD总线上的通信是基于命令和数据流,这些数据流由一个开始位发起,并由一个停止位终止

1.2 传输

①command

- 0起始1结束

- crc,7位,是计算出来的,最后进行check

- 数据38bit,总长48bit

②response

- 四种response类型R1 R3 R6 R2

③数据传输

-

两种传输方法,一线和四线

-

一线数据排布

-

四线数据排布

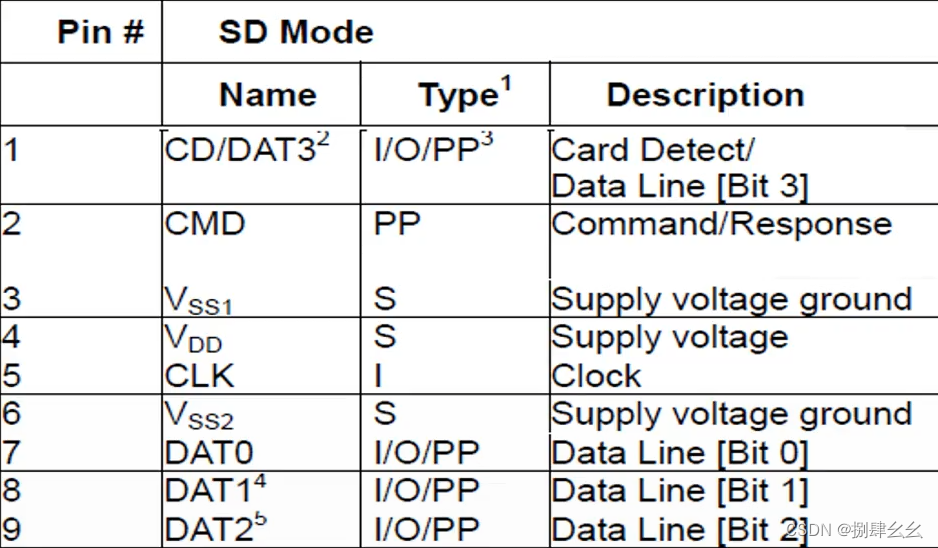

1.3 接口

- 上面说了SD协议是6个pin脚,而这个封装却9个,实际上多了3个电源的pin

- wp就是1.1中提到的机械开关

1.4 reg

- 每一张sd卡都有它的寄存器信息,下面展开介绍

名字 位宽 描述 CID 128 相当于SD卡的身份证 RAC 16 SD卡的相对地址 ,让host知道SD卡的位置 DSR 16 (不重要) CSD 128 SD卡的操作条件信息有关 SCR 64 配置寄存器 OCR 32 操作寄存器 SSR 512 状态寄存器,卡的属性特性 CSR 32 状态寄存器,卡的状态 1.5 SD内部

- 上电复位 power on reset

- 软件也可以通过命令复位

1.6 两种command

- 主机和卡之间的所有通信都由主机控制,而主机发送两种类型的命令:广播和地址命令(point2point)

- 广播命令广播命令适用于所有卡,其中一些命令需要响应

- 地址命令被发送到寻址卡并引起该卡的响应

1.7 卡状态

- 我们设计的是AHB_SD_HOST控制器,但是也需要了解SD卡内部的状态

- 这样才能考虑好设计的情况

- programing存在的理由就是数据先缓存,然后再programing到非易失性的mem中

1.8 插卡识别

- 上电处于idle状态,发送CMD0,检查host提供的电压

- 继续发CMD8,如果SD卡有response,则电压适合,若没有,则不会工作

- 接着发ACMD41,检查SD卡能否兼容host

- 接着发CMD2进行身份验证,也就是get CID

- 再发CMD3进行二重认证,也就是get RCA

- 最后进入数据阶段的stand-by状态

1.9 传输状态

- SD卡的传输状态

- SD卡中有好多CMD,但是在host中我们不可能全部兼容设计,只设计一些常用的CMD

1.10 总线宽度选择

- 宽总线(4Bit 宽)操作模式可以通过命令 ACMD6 来选定和取消

- 上电或者 GO_IDLE(CMD0)命令 后,默认的总线宽度是1Bit.

- 如果想要改变总线宽度,需要具备下面两个条件:

a) 卡处于 transfer 状态

b) 卡没有被锁定 (锁定的卡会认为 ACMD6 是无效命令)

1.11 读写数据

- 当没有数据传输的时候,DAT 总线电平被拉高

- 一个传输的“数据块”包含了起始位(1bit 或者 4bit低),和后面连续的数据流

- 数据流包含了有效数据

- 数据流后面是结束位

- 块数据传输的有效性是通过CRC校验值来进行的

- 从 SD 卡读数据的操作有可能被断电中止,即使突然断电或者移除,SD 卡都会确保数据

不被损坏,但是主机发起的写操作和擦除操作时不行

BLOCK_LEN_ERROR 或者 ADDRESS_ERROR发生的时候,读写命令是不能执行的,并且也不能 数据传输。

1.12 循环冗余码(CRC)

CRC 适用于保护 SD 总线上的 SD 卡命令,响应和数据传输免于出错的。命令线上,每个命令

都会产生 CRC,而每个响应也都会检查 CRC。对于数据块来说,每一个传输的块都会产生 CRC。

CRC 的产生和检查描述如下:-

CRC7

CRC7 的检测是用于所有的命令,所有的响应(除了 R3),以及 CSD 和 CID 寄存器

生成电路:

-

CRC16

使用数据线的时候,CRC16 用于有效保护块传输模式

CRC16 应该单独的用在每个数据线上,即使是宽总线模式,也要每跟数据线单独校验

生成电路

1.13 命令格式

- 所有的命令都有一个固定的长度 48bit,在 25MHz 的频率下需要 1.92us,在 50Mhz 的频

率下需要 0.96us

- 来看看具体的CMD基础命令

- 具体的其他命令还是要在sd2.0协议的datasheet里面去看

1.14 卡状态转换表

1.15 响应

-

所有的响应都是通过 CMD 线发送的;响应总是从 bit 串最左边的 bit 开始发送,对应响

应码;响应的长度取决于响应的类型 -

R1:正常响应命令,和command格式几乎一样

-

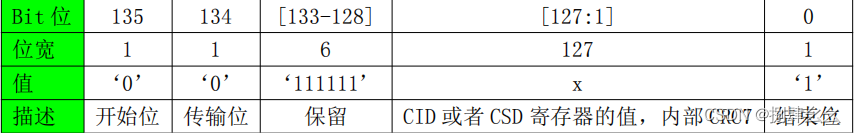

R2:CID、CSD 寄存器,长度为 136bit;CID 寄存器的内容作为 CMD2 和 CMD10 的响应发;CSD 寄存器的内容作为 CMD9 的响应发送;只传输 CID 和 CSD 寄存器的[127:1]位,这些寄存器的第[0]位被响应的结束位替代了

-

R3:长度 48bit,OCR 寄存器的值作为 ACMD41 的响应发送

-

R6:发布的 RCA 寄存器响应,长度 48bit。[45:40]是响应的命令号,这里就是‘000011’,即CMD3;参数中的 16位MSB 用于产生 RCA 号

-

R7:长度 48bit;卡支持的电压信息通过 CMD8 的响应发送;Bit[19:16]表明卡支持的电压范围;卡接受提供的电压范围就返回 R7 响应;卡会在响应的参数中返回电压范围和检查模式

1.16 时序

- 时序图采用的图例和缩写:P 和 Z 的不同之处就是,P 是被主机输出驱动的各个卡主动拉高的,Z 是分别被上拉电阻 Rcmd 和 Rdat 拉高,P 受噪音影响更小写

- 卡识别时序:CMD2 和 ACMD41 的时序如下。命令后跟着两个 Z bit(允许总线切换方向的时间),接着是响应卡发出的 P bit;卡响应主机命令的起始在 Nid 时钟周期后

- 分配卡的相对地址RCA:SEND_RELATIVE_ADDR(CMD3)命令时序如下;主机命令和响应之间的最小延迟是 Ncr 个时钟周期

- 数据传输模式:当卡发布自己的 RCA 后,将会切换到数据传输模式“transfer”,这个响应时序是除了 ACMD41 和 CMD2之外,所有主机命令响应的时序

- 响应后到下个命令的时序:主机在最少 Nrc 个时钟周期后可以继续发送下一个命令

- 无响应时的下一个命令时序:主机在最少 Ncc 个时钟周期后可以继续发送下一个命令

- 单块读(single block read):序列以单块读命令(CMD17)开始,CMD17 在参数中指出了起始地址,这里又多了一个Nac的周期数

- 多块读(multiple block read):多块读模式中,在主机读命令之后,卡发送一个连续的数据块流;通过 CMD12 来中止

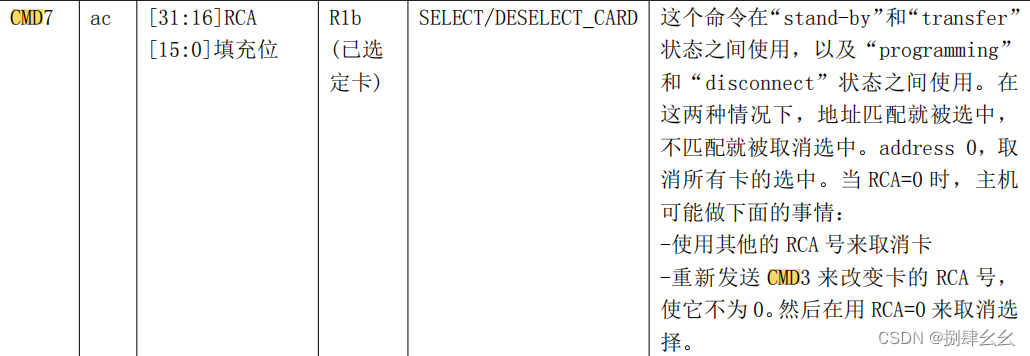

- 单块写:主机通过命令 CMD7 来选择一个卡进行写操作;主机通过命令 CMD16来设置需要进行块传输的有效块长度;写操作的基础总线时序。以 CMD24 作为开始,标明起始地址;卡通过 CMD线回应;主机的数据传输在收到响应后的 Nwr 时钟周期后开始

- 多块写:有busy就等待,没有就继续发数据,也是使用CMD12结束

- 上述的参数N表

2.SD_HOST控制器设计架构

AHB_SD_HOST总的来说就是产生符合SD协议的命令和数据的操作,整体架构如下

2.1 需要完成的功能

- 控制器AHB总线接口数据处理符合AMBATM Specification(Rev 2.0)协议

- SD SpecificationsVersion 2.00

- 具备多个控制配置寄存器,可以实现对命令和数据的控制

- Built-in DMA,支持AHB总线字( word) single & incr模式传输

- 支持对卡的单块、多块读写和读写加速

- 和SDIO模块共享FIFO和内嵌DMA模块

- 内含相应寄存器和分频电路,实现SD总线的时钟控制

- 读操作时,硬件停时钟功能(省点功耗)

2.2 软硬件划分

- 软件:说白了就是寄存器的配置以及时序的配置

- 硬件:

①AHB DMA 的一些接口

②SD总线接口

③命令数据处理模块

2.3 模块简述

- sd_if模块:ahb slave接口模块,内含控制寄存器,供CPU访问,决定HOST的工作模式;

- sd_clk模块:hclk分频电路,作为HOST模块时钟输入

- sd_cmd_fsm模块:命令操作控制模块,控制sd_cmd_send_shift_register和 sd_cmd_receice_shift_register模块;

- sd_cmd_send_shift_register模块:sd命令发送端 口;

- sd_cmd_receive_shift_register模块:sd卡命令返回端口;

- sd_data_fsm模块:数据操作控制模块,控制sd_data_send_shift_register和sd_data_receice_shift_register模块;

- sd_data_send_shift_register模块:sd数据发送端;

- sd_data_receive_shift_register模块:sd数据输入端口;

- FIFO模块:数据缓存模块;

- DMA模块:数据搬移模块;

3.总线接口

3.1 AHB总线信号

AHB总线具体的不多阐述了,已经写在ahb2sram的文章里面了,下面是具体的接口

- AHB_Slave

- AHB_Master (DMA)

3.2 SD总线

- cmd_out、rsp_in、cmd_oe构成一个pad

4.SD_HOST寄存器介绍

4.1 CLK_EN_SPEED_UP_ADDR

- size:32

- addr offset:0x50

- read/write:可读可写

4.2 SOFTWARE_RESET_REGISTER_ADDR

- size:32

- addr offset:0x04

- read/write:可读可写

4.3 ARGUMENT_REGISTER_ADDR

- size:32

- addr offset:0x08

- read/write:可读可写

- ARGUMENT就是下表的参数

4.4 COMMAND_REGISTER_ADDR

- size:32

- addr offset:0x0c

- read/write:可读可写

4.5 BLOCK_SIZE_REGISTER_ADDR

- size:32

- addr offset:0x10

- read/write:可读可写

4.6 BLOCK_COUNT_REGISTER_ADDR

- size:32

- addr offset:0x14

- read/write:可读可写

4.7 TRANSFER_MODE_REGISTER_ADDR

- size:32

- addr offset:0x18

- read/write:可读可写

4.8 RESPONSE0_REGISTER_ADDR

- size:32

- addr offset:0x1c

- read/write:只读

4.9 RESPONSE1_REGISTER_ADDR

- size:32

- addr offset:0x20

- read/write:只读

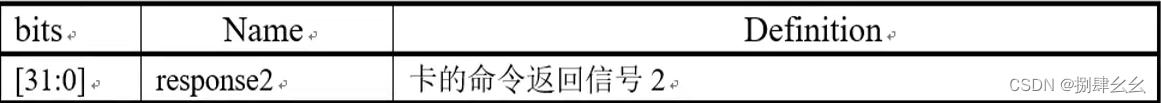

4.10 RESPONSE2_REGISTER_ADDR

- size:32

- addr offset:0x24

- read/write:只读

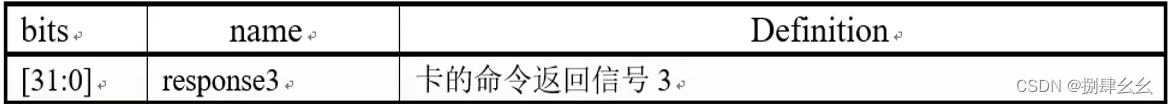

4.11 RESPONSE3_REGISTER_ADDR

- size:32

- addr offset:0x28

- read/write:只读

4.12 READ_TIMEOUT_CONTROL_REGISTER_ADDR

- size:32

- addr offset:0x2c

- read/write:可读可写

4.13 INTERRUPT_STATUS_REGISTER_ADDR

- size:32

- addr offset:0x30

- read/write:只读

4.14 INTERRUPT_STATUS_MASK_REGISTER_ADDR

- size:32

- addr offset:0x34

- read/write:可读可写

- 对应上个寄存器表中的中断屏蔽位

4.15 INT_GEN_REG_ADDR

- size:32

- addr offset:0x48

- read/write:可读可写

4.16 CLR_INT_REG_ADDR

- size:32

- addr offset:0x4c

- read/write:可读可写

4.17 DMA_CTRL_ADDR

- size:32

- addr offset:0x44

- read/write:可读可写

4.18 DAM_ADDR_ADDR

- size:32

- addr offset:0x40

- read/write:可读可写

5.RTL代码

5.1 sd_if.v

- 作用:

下面是主要的RTL设计- 寄存器配置

- 地址写

- 地址读

- DMA

- response

具体RTL设计代码:

5.2 待续

-

相关阅读:

vue中子组件如何向父组件传值与父组件如何向子组件传值

JAVA基础(三十四)——异常处理

Hudi第二章:集成Spark(二)

英语学习目标与计划

基于Zookeeper搭建Kafka高可用集群(实践可用)

OD1 敏捷背后的思路

交换机之间配置手动|静态链路聚合

安卓与js交互

【MyBatis】缓存——使查询变得快快快!

80-Java的Map集合:概述、API、遍历方式

- 原文地址:https://blog.csdn.net/qq_38502780/article/details/125458977